次世代半導体とは?パッケージ技術はなぜ必要?強みや将来性を解説

スマートフォンの高性能化、AI技術の急速な発展、電気自動車の普及——これらすべてを支えているのが半導体技術です。しかし、従来の半導体では限界が見え始め、より高性能で効率的な「次世代半導体」への注目が高まっています。

特に重要なのが「パッケージ技術」です。半導体チップを保護し、外部回路と接続するこの技術は、単なる「包装」を超えて、半導体の性能を最大限に引き出す鍵となっています。微細化の限界に直面する中、パッケージレベルでの革新が、処理速度の向上、消費電力の削減、そして新たな機能の実現を可能にしているのです。

本記事では、次世代半導体とは何か、なぜパッケージ技術が不可欠なのか、そして日本企業が持つ独自の強みと将来性について、分かりやすく解説していきます。半導体業界の最前線で起きている技術革新を通じて、私たちの生活がどのように変わっていくのかを見ていきましょう。

次世代半導体とは?なぜ必要?

.jpg)

次世代半導体とは、従来のシリコンを主材料とした半導体技術の物理的限界を突破するために開発が進められている新世代の半導体技術の総称です。これまでの半導体は、回路の微細化によって性能向上を実現してきましたが、原子レベルまで小さくなった現在、従来の手法では限界に達しつつあります。

このような状況で次世代半導体が必要となる背景には、デジタル社会の急速な進展があります。AI、IoT、5G通信、自動運転などの技術革新により、膨大なデータを瞬時に処理し、かつ省電力で動作する半導体への需要が飛躍的に高まっています。従来のシリコン半導体では、これらの要求を満たすことが困難になってきているのです。

そこで注目されているのが、シリコンカーバイド(SiC)や窒化ガリウム(GaN)などの新材料を用いた化合物半導体、三次元積層技術、さらには量子コンピュータ向けの量子半導体などです。これらの新しい材料や構造、製造技術により、より高い処理能力と効率性を両立させることが可能となり、次世代のデジタル社会を支える基盤技術として期待されています。

次世代半導体の主な方向性

.jpg)

次世代半導体の方向性は、従来の「ムーアの法則」に代表される微細化の限界が近づく中で、新たな技術革新によって性能向上や機能多様化を目指す多岐にわたるアプローチが模索されています。主な方向性は以下の通りです。

新素材の活用(化合物半導体・ワイドバンドギャップ半導体)

次世代半導体においては、従来のシリコン(Si)半導体が持つ物理的限界を打破し、さらなる高性能化や新機能の実現を目指す上で、シリコンに代わる新しい材料の活用が不可欠となっています。

これらの新材料を用いることで、シリコンでは実現が難しかった特性、具体的には「高速性、高耐圧性、低損失、高温動作」などを実現し、幅広い分野での革新が期待されています。

炭化ケイ素

炭化ケイ素は、シリコンと炭素の化合物で構成される次世代半導体材料です。従来のシリコン半導体と比べて約10倍の絶縁破壊電界強度を持ち、高温・高電圧環境での動作が可能という特徴があります。また、熱伝導率が高く、電力損失を大幅に削減できるため、エネルギー効率の向上に大きく貢献します。

主な用途としては、電気自動車のインバータ、太陽光発電システムのパワーコンディショナー、産業用モーター制御装置などの電力変換装置で活用されています。特に電気自動車分野では、SiC素子の採用により航続距離の延長と充電時間の短縮が実現されており、カーボンニュートラル社会の実現に向けた重要な技術として注目されています。

窒化ガリウム

窒化ガリウムは、ガリウムと窒素の化合物からなる化合物半導体で、高い電子移動度と優れた高周波特性を持つことが特徴です。シリコンと比較して約3倍の電子移動度を有し、高速スイッチング動作が可能であるため、高効率な電力変換と高周波信号の処理に適しています。また、小型化と軽量化も実現できます。

用途面では、スマートフォンの急速充電器、ノートパソコンのACアダプター、データセンターの電源装置などの小型高効率電源機器で広く採用されています。さらに、5G基地局の高周波増幅器、レーダーシステム、衛星通信機器などの高周波アプリケーションでも重要な役割を果たしており、次世代通信インフラの発展に不可欠な材料となっています。

酸化ガリウム

酸化ガリウムは、約4.8eVという極めて大きなバンドギャップを持つ超ワイドバンドギャップ半導体材料です。この特性により、従来の半導体材料では実現困難な超高耐圧・超低損失の電力制御が可能となります。また、大型の単結晶基板を比較的安価に製造できるという製造面での優位性も持っています。

現在は研究開発段階にありますが、将来的には超高圧電力系統の制御装置、電力グリッドの安定化装置、宇宙・航空機器の電源システムなどの極限環境での応用が期待されています。特に、再生可能エネルギーの大規模導入に伴う電力系統の複雑化に対応するため、次世代の電力インフラを支える基幹技術として研究が活発化しています。

ダイヤモンド半導体

ダイヤモンド半導体は、炭素原子が規則正しく配列したダイヤモンド結晶を基材とする究極の半導体材料です。5.5eVという最大級のバンドギャップと、最高レベルの熱伝導率、化学的安定性を併せ持ちます。これにより、極高温・極高電圧・強放射線環境での動作が可能で、理論上は他の半導体材料を大幅に上回る性能を発揮できます。

現在は製造技術の課題により実用化には至っていませんが、将来的には原子力発電所や宇宙探査機器など、極限環境での電子機器、超高効率パワーデバイス、量子コンピュータの構成要素などへの応用が構想されています。

製造技術の確立により、現在の半導体技術の常識を覆す革新的なデバイスの実現が期待されており、長期的な技術発展の方向性を示す重要な材料として位置づけられています。

関連記事:ダイヤモンド半導体とは?何がすごい?メリット・デメリットや将来的な実用化について

微細化・積層化技術の進化

次世代半導体における微細化と積層化技術の進化は、シリコン半導体においても性能向上のための最も重要なアプローチであり、ムーアの法則の継続と、その限界を超えるための新たな道を切り開いています。

微細化

微細化とは、半導体チップ上に形成される回路パターン(配線幅や素子間隔)をより小さくする技術のことです。現在の最先端プロセスでは3ナノメートル(nm)レベルまで到達しており、これは原子数個分の幅に相当する極限の精密さです。微細化により、同じ面積のチップにより多くのトランジスタを搭載でき、処理性能の向上と消費電力の削減を同時に実現できます。

技術的には、従来の光リソグラフィーに加えて、極紫外線(EUV)リソグラフィーや電子線描画技術などの最先端製造技術が駆使されています。また、FinFET(フィンフェット)やGAA(Gate-All-Around)といった三次元構造のトランジスタ設計により、電流制御の精度を高めながら微細化を推進しています。

しかし、物理的限界に近づいているため、今後は新材料の導入や新しい回路設計手法との組み合わせが重要になっています。微細化は「ムーアの法則」として知られる半導体業界の発展を支えてきた根幹技術であり、スマートフォンからスーパーコンピュータまで、あらゆる電子機器の高性能化を可能にしています。

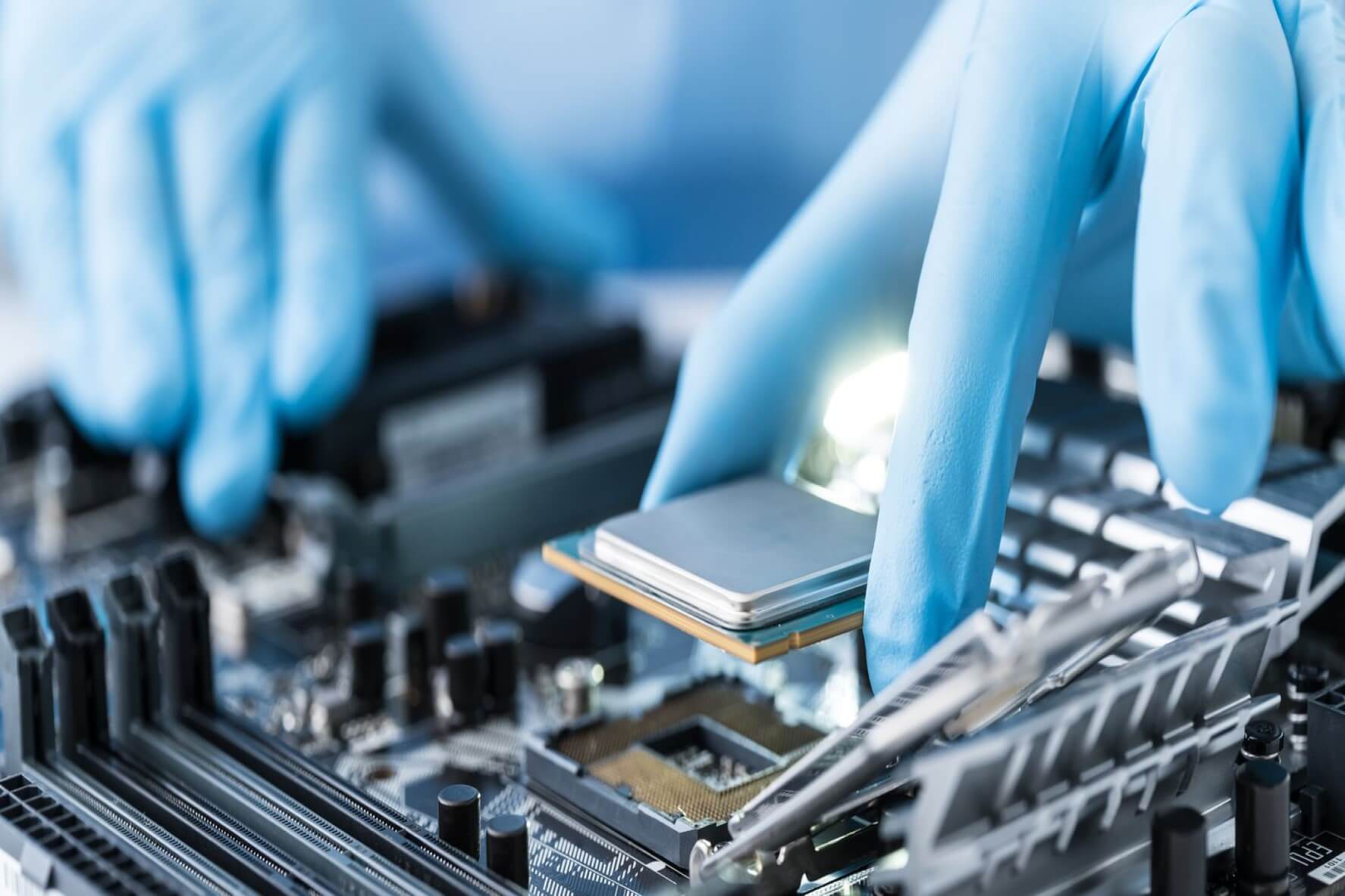

積層化(異種集積化、3Dパッケージング)

積層化技術は、複数の半導体チップを垂直方向に重ね合わせることで、限られた実装面積でより高い機能と性能を実現する技術です。従来の平面的なチップ配置から立体的な構造へと発想を転換し、システム全体の小型化と高性能化を両立させます。特に異種集積化では、プロセッサ、メモリ、センサーなど異なる機能を持つチップを一つのパッケージ内に統合することで、データ転送の高速化と消費電力の削減を実現しています。

3Dパッケージング技術では、TSV(Through Silicon Via:シリコン貫通電極)やマイクロバンプなどの高密度接続技術により、チップ間の電気的接続を行います。また、各層の熱管理も重要な課題となっており、高効率な放熱設計が求められています。この技術により、スマートフォンのカメラモジュール、高性能メモリ(HBM:High Bandwidth Memory)、AI処理用チップセットなどで実用化が進んでいます。

将来的には、チップレット技術と組み合わせることで、必要な機能だけを選択的に組み合わせたカスタマイズ可能な半導体システムの実現が期待されており、次世代コンピューティングの基盤技術として注目されています。

新原理に基づく半導体の研究

次世代半導体の研究開発は、従来のシリコン半導体の微細化や積層化、新材料の導入といった「延長線上」のアプローチに加えて、全く新しい物理原理に基づいた半導体や計算方式の探求も活発に行われています。

これらはまだ実用化には至っていませんが、将来のコンピューティングを根本から変える可能性を秘めており、長期的な視点での基礎研究が進められています。

量子コンピュータ

量子コンピュータは、従来のコンピュータが「0」または「1」の二進法で情報を処理するのに対し、量子力学の原理を活用して「0と1の重ね合わせ状態」で計算を行う革新的なコンピューティング技術です。量子ビット(qubit)と呼ばれる情報単位は、古典的なビットとは異なり、複数の状態を同時に保持できるため、膨大な組み合わせを並列処理することが可能になります。

技術的には、超伝導回路、イオントラップ、光子、トポロジカル量子状態など、様々な物理現象を利用した量子ビットの実現方法が研究されています。特に超伝導量子コンピュータでは、極低温環境下で動作する超伝導素子を用いて量子状態を制御し、量子もつれや量子干渉といった量子力学特有の現象を計算に活用します。

現在、IBMやGoogle、量子コンピュータ専業企業などが数百量子ビット規模のシステムを開発しており、将来的には暗号解読、新薬開発のシミュレーション、金融リスク計算、人工知能の学習アルゴリズムなど、従来のコンピュータでは現実的な時間では解けない複雑な問題の解決が期待されています。ただし、量子状態は外部ノイズに非常に敏感であるため、量子エラー訂正技術の確立が実用化への大きな課題となっています。

光半導体

光半導体は、電気信号の代わりに光(フォトン)を用いて情報の処理・伝送・記録を行う次世代半導体技術です。従来の電子ベースの半導体が電子の移動による電気信号で動作するのに対し、光半導体は光の特性を活用することで、超高速データ処理と大容量通信を実現します。光は電気信号よりもはるかに高速で伝播し、電磁干渉の影響を受けにくく、並列処理にも適しているという優位性があります。

技術的には、シリコンフォトニクス、化合物半導体レーザー、光変調器、光検出器などの要素技術を組み合わせて、光信号の発生・制御・検出を行います。特にシリコンフォトニクスでは、従来の半導体製造技術を応用して光回路をチップ上に集積することで、小型化と量産化を両立させています。

現在、データセンター間の高速光通信、AI処理における大容量データ転送、LiDAR(光による距離測定)システムなどで実用化が進んでいます。将来的には、光コンピューティングによる超並列処理、光ニューラルネットワークによるAI処理の高速化、さらには量子光学技術と組み合わせた量子通信システムなどへの応用が期待されており、次世代情報社会の基盤技術として重要な位置を占めています。

関連記事:光半導体とは?実用化はいつ?仕組みや将来性について解説

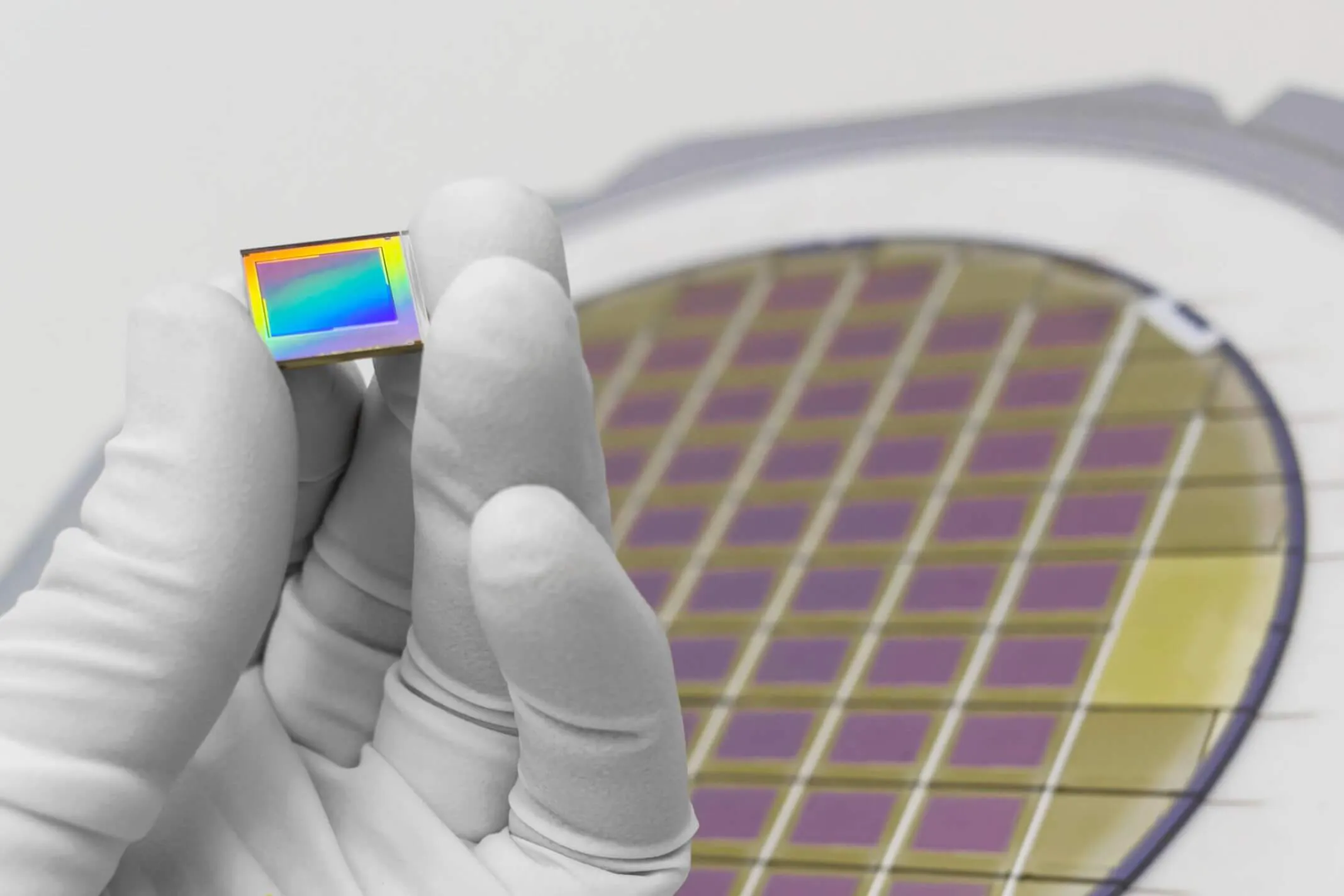

次世代半導体パッケージ技術とは

「次世代半導体パッケージ」とは、複数の半導体チップや異なる種類の素子を、より高密度に、そして高性能に接続・集積するための技術と構造の総称です。これは、半導体の性能向上において、微細化と並ぶ、あるいはそれ以上に重要な柱として位置づけられています。

なぜ次世代半導体パッケージが必要?

半導体産業は長らく「ムーアの法則」に基づき、トランジスタの微細化を進めることで性能向上とコストダウンを図ってきました。しかし、現在、この微細化は物理的な限界(原子レベルのサイズ)に近づき、同時に製造コストも指数関数的に増大するという課題に直面しています。

このような状況下で、チップ単体の性能向上だけでは、今後のコンピューティング需要を満たすことが難しくなってきました。そこで、注目されているのが「パッケージング」技術です。これは、まるでレゴブロックのように、機能ごとに分かれた複数のチップ(CPU、GPU、メモリ、特定機能アクセラレータなど)を効率的かつ高性能に組み合わせることで、半導体全体の性能を左右する重要な要素となっています。

ムーアの法則の限界

ムーアの法則とは、半導体の集積密度が約2年ごとに倍増するという経験則で、1965年にインテル創設者のゴードン・ムーアが提唱しました。これまで約50年間にわたって半導体業界の発展を牽引してきましたが、現在3ナノメートルプロセスに到達し、物理的・経済的限界に直面しています。原子レベルの微細化では、量子効果によるリーク電流の増大、製造ばらつきの拡大、製造コストの指数関数的増加といった問題が顕在化しています。

従来は微細化により性能向上とコスト削減を同時に実現できましたが、現在では微細化のメリットが薄れ、むしろ製造コストが急激に上昇しています。例えば、3nmプロセスの製造装置には数百億円の投資が必要となり、経済合理性の観点からも限界に達しつつあります。

このため、単純な微細化に依存しない新たなアプローチとして、複数のチップを効率的に組み合わせる次世代パッケージ技術が注目されています。パッケージレベルでの統合により、微細化に頼らずとも性能向上を実現し、半導体業界の持続的発展を可能にする技術として期待されています。

歩留まりの悪化

歩留まりとは、製造工程において正常に動作する良品チップの割合を示す指標です。半導体の微細化が進むにつれて、製造プロセスの複雑化と精密度の要求が高まり、わずかな製造ばらつきでも不良品となる確率が増加しています。特に最先端プロセスでは、原子レベルの精度が要求されるため、ちりやほこり、温度変化、装置の微小な振動などが直接的に歩留まりに影響します。

大型の単一チップを製造する場合、チップ面積が大きいほど欠陥が含まれる確率が高くなり、歩留まりは指数関数的に悪化します。例えば、高性能プロセッサのような大型チップでは、歩留まりが30%以下になることも珍しくありません。これは製造コストの大幅な増加を意味し、最終製品価格の上昇につながります。

次世代パッケージ技術では、機能別に小型化したチップレット(小さなチップ)を個別に製造し、パッケージレベルで統合することで、各チップの歩留まりを向上させながら、システム全体としては大型チップと同等の性能を実現できます。この手法により、製造コストの抑制と性能向上を両立させることが可能になります。

異なる技術の統合の難しさ

現代の電子システムでは、デジタル処理、アナログ回路、高周波通信、センサー、メモリなど、異なる機能を持つ回路技術の統合が不可欠です。しかし、これらの技術は最適な製造プロセスや材料が大きく異なるため、単一のチップ上に統合することは技術的に困難で、性能面でも妥協が必要になります。例えば、デジタル回路は微細化による高集積化が重要ですが、アナログ回路は電気的特性の安定性を重視するため、必ずしも最先端プロセスが適しているとは限りません。

また、高周波回路では低損失な材料が必要で、センサー回路ではMEMS(微小電気機械システム)技術が必要になるなど、それぞれに特化した製造技術が求められます。従来の単一チップでこれらすべてを実現しようとすると、各機能に最適化できず、システム全体の性能が制限されてしまいます。

次世代パッケージ技術では、各機能に最適化された異なるプロセスで製造されたチップを、パッケージレベルで高密度に統合することで、この問題を解決します。これにより、各技術領域で最高性能を発揮しながら、システム全体としても最適化された製品を実現することが可能になります。

データ転送のボトルネック

現代の高性能システムでは、プロセッサの処理能力の向上に対して、チップ間や基板上での信号伝送速度が追いつかない「データ転送のボトルネック」が深刻な問題となっています。従来のワイヤボンディングや基板配線では、信号の遅延、電力消費、ノイズの増大により、システム全体の性能が制限されてしまいます。特にAI処理や高速データ処理では、大容量のデータを瞬時に転送する必要があり、この問題がより顕著になっています。

例えば、プロセッサとメモリ間のデータ転送では、物理的な距離が長くなるほど信号遅延が増加し、高速動作の妨げとなります。また、高速信号ほど電力消費が大きくなり、発熱問題も深刻化します。次世代パッケージ技術では、TSV(シリコン貫通電極)やマイクロバンプなどの高密度接続技術により、チップ間の距離を大幅に短縮し、接続数を大幅に増やすことができます。

これにより、データ転送の高速化、低消費電力化、低ノイズ化を同時に実現し、システム全体の性能向上に貢献します。特に3D積層技術では、垂直方向の短距離接続により、従来の配線では実現困難な超高速データ転送が可能になります。

チップレット技術

チップレット技術は、従来の大型SoC(System on Chip)を機能別の小さなチップに分割し、それぞれを最適なプロセスで製造してから一つのパッケージ内で統合する革新的なアプローチです。CPUコア、GPUコア、メモリコントローラ、I/Oインターフェースなど、異なる機能を持つチップレットを組み合わせることで、各機能に最適化された製造プロセスを選択できるため、性能向上とコスト削減を同時に実現できます。

この技術の最大の特徴は、設計の柔軟性と製造効率の向上にあります。例えば、CPUコアには最先端の微細プロセスを適用して高性能化を図る一方、I/O回路には成熟したプロセスを使用してコストを抑制できます。また、小型化により各チップレットの歩留まりが向上し、全体の製造コストも削減されます。

現在、AMDのRyzenプロセッサやEPYCサーバー向けCPUで実用化が進んでおり、インテルも同様の技术を採用しています。将来的には、顧客の要求に応じて必要な機能のチップレットのみを選択組み合わせるカスタマイズ可能なシステムの実現が期待されており、半導体業界の新たなビジネスモデルとしても注目されています。

ヘテロジニアス・インテグレーション

ヘテロジニアス・インテグレーションは、ロジック回路、メモリ、アナログ回路、MEMS(微小電気機械システム)など、異なる種類や製造プロセスで作られた半導体チップを一つのパッケージ内に統合する先進技術です。従来の単一チップでは実現困難だった多様な機能の最適化を可能にし、各チップが本来持つ最高性能を発揮させながらシステム全体の小型化と高機能化を実現します。

この技術の核心は、異種技術間の効率的な接続と協調動作にあります。デジタル処理には最先端の微細プロセスを適用し、アナログ回路には電気特性に優れた成熟プロセスを使用し、センサー部品にはMEMS技術を採用するといったように、各機能に最適な技術を選択できます。現在、スマートフォンのカメラモジュールでは、イメージセンサー、画像処理チップ、アナログフロントエンドが統合され、高画質と小型化を両立しています。

また、IoTデバイスでは、マイクロプロセッサ、無線通信チップ、各種センサーが一体化されており、多機能でありながら省電力動作を実現しています。将来的には、AI処理、通信、センシング機能を統合したオールインワンチップの開発が期待されており、次世代電子機器の核心技術として位置づけられています。

2.5D/3Dパッケージング

2.5D/3Dパッケージングは、従来の平面的なチップ配置から立体的な構造へと発展させた高密度実装技術です。2.5Dパッケージングでは、複数のチップをインターポーザーと呼ばれる中間基板上に配置し、微細配線により高速接続を実現します。一方、3Dパッケージングでは、チップを垂直方向に直接積層し、TSV(シリコン貫通電極)やマイクロバンプを用いて層間接続を行います。

この技術により、限られた実装面積でより多くの機能を集積でき、チップ間の物理的距離を大幅に短縮することで信号遅延の削減と消費電力の低減を実現します。特に3D構造では、データ転送距離が従来の数十分の一になるため、超高速データ処理が可能になります。現在、高性能メモリのHBM(High Bandwidth Memory)では、複数のDRAMチップを垂直積層してメモリ容量と帯域幅を大幅に向上させています。

また、スマートフォンのカメラモジュールでは、イメージセンサーと画像処理チップを積層することで、小型化と高画質化を両立しています。今後は、AI処理チップとメモリの一体化や、センサーと処理回路の統合により、さらなる高性能化と小型化が期待されています。

次世代半導体の強み

.jpg)

次世代半導体の強みを説明するために、いくつかの側面から情報を検索します。 次世代半導体は、従来のシリコン半導体の限界を乗り越え、様々な分野で革新をもたらす強力な技術です。その主な強みは、

高性能化・高速化

次世代半導体による高性能化・高速化は、処理能力の飛躍的向上とデータ転送速度の大幅な改善を実現します。新材料の活用により、従来のシリコン半導体では達成困難な高速スイッチング動作が可能になり、特に窒化ガリウム(GaN)では約3倍の電子移動度により超高速処理を実現しています。また、3D積層技術やチップレット構成により、プロセッサコア数の大幅増加と並列処理性能の向上が可能になります。

量子コンピュータ技術では、従来の逐次処理とは根本的に異なる量子並列処理により、特定の計算問題において指数関数的な処理速度向上を実現できます。光半導体技術では、光速による信号伝送と光の並列性を活用することで、電気信号では不可能な超高速データ処理が可能になります。

さらに、ヘテロジニアス・インテグレーションにより、各機能に最適化されたチップを組み合わせることで、システム全体として従来の単一チップでは実現できない高性能を発揮できます。これらの技術により、AI処理、リアルタイム画像解析、高頻度取引システムなど、極めて高い処理性能が要求される分野での革新的な性能向上が期待されています。

省エネルギー化・高効率化

次世代半導体の省エネルギー化は、新材料の優れた電気特性と先進的なパッケージ技術により実現されます。炭化ケイ素(SiC)や窒化ガリウム(GaN)などのワイドバンドギャップ半導体は、従来のシリコンと比較して電力損失を大幅に削減でき、電力変換効率を95%以上まで向上させることが可能です。これにより、電気自動車の航続距離延長や産業機器の省エネルギー化に大きく貢献しています。

3D積層技術では、チップ間の配線距離を短縮することで信号伝送に必要な電力を大幅に削減し、システム全体の消費電力を従来の半分以下に抑制できます。また、チップレット技術により、使用しない機能部分の電源を個別に制御できるため、必要最小限の電力消費で動作させることが可能になります。光半導体技術では、電気信号の代わりに光を使用することで、長距離データ伝送における電力損失をほぼゼロに近づけることができます。

さらに、AI処理においても、専用の低消費電力チップと効率的なデータフロー設計により、従来の汎用プロセッサと比較して数十倍の電力効率を実現し、持続可能な社会の実現に貢献しています。

小型化・軽量化

次世代半導体による小型化・軽量化は、垂直統合技術と高密度実装により劇的な進歩を遂げています。3D積層技術では、従来は平面上に配置していた複数のチップを垂直方向に重ねることで、実装面積を従来の数分の一に削減できます。例えば、スマートフォンのメモリシステムでは、8層から16層の積層により、同一性能を維持しながら実装面積を約80%削減することが可能になっています。

ヘテロジニアス・インテグレーションにより、従来は基板上に分散配置していた異なる機能のチップを一つのパッケージ内に統合することで、システム全体の大幅な小型化を実現できます。また、新材料の活用により、同一性能をより小さなチップサイズで実現でき、パッケージ全体の軽量化にも貢献します。チップレット技術では、必要な機能のみを選択的に統合することで、無駄な回路を排除し、最適化されたコンパクトなシステムを構築できます。

これらの技術により、ウェアラブルデバイス、IoT機器、ドローンなど、小型軽量化が重要な製品分野において、従来では実現困難だった高機能と携帯性の両立が可能になり、新たな製品カテゴリーの創出にも寄与しています。

高い耐性・信頼性

次世代半導体は、過酷な環境条件下でも安定した動作を実現する高い耐性と信頼性を備えています。炭化ケイ素(SiC)や酸化ガリウム(Ga₂O₃)などの新材料は、従来のシリコンでは動作困難な高温環境(200℃以上)での安定動作が可能で、自動車のエンジンルームや産業機器の高温環境での使用に適しています。また、これらの材料は放射線に対する耐性も高く、宇宙空間や原子力施設などの過酷な環境での利用が期待されています。

ダイヤモンド半導体は究極の耐環境性を持ち、極高温・強放射線・強酸性環境でも動作可能な理論的特性を有しています。パッケージ技術の観点では、3D積層やヘテロジニアス・インテグレーションにより、冗長性を持つシステム設計が可能になり、一部の回路に故障が発生してもシステム全体としては動作を継続できます。

また、チップレット技術では、故障した機能部分のみを交換することで、システム全体の寿命延長と保守性向上を実現できます。これらの特性により、航空宇宙、医療機器、社会インフラなど、高い信頼性が要求される分野での採用が進んでおり、社会の安全性と持続性の向上に大きく貢献しています。

柔軟性とコスト効率

次世代半導体技術は、設計の柔軟性向上と製造コストの最適化を同時に実現します。チップレット技術では、異なる機能を持つ小さなチップを組み合わせることで、顧客の要求に応じたカスタマイズが容易になり、必要な機能のみを選択的に統合できます。これにより、オーバースペックによる無駄を排除し、コスト効率の高いシステムを構築できます。

また、各チップレットを異なるプロセスノードで製造できるため、性能が重要な部分には最先端プロセスを、コストが重要な部分には成熟プロセスを適用する最適化が可能です。

ヘテロジニアス・インテグレーションでは、既存の設計資産を再利用しながら新機能を追加できるため、開発期間の短縮と開発コストの削減を実現できます。小型チップの歩留まり向上により、従来の大型チップと比較して製造コストを大幅に削減でき、特に複雑な機能を持つシステムでその効果が顕著に現れます。

さらに、標準化されたインターフェースにより、異なるメーカーのチップを組み合わせることも可能になり、サプライチェーンの柔軟性と競争力向上に寄与します。これらの特徴により、多様な市場ニーズに迅速かつ効率的に対応でき、半導体業界全体の持続的成長を支える基盤技術として期待されています。

次世代半導体のシェア

.jpg)

次世代半導体、特にSiC(炭化ケイ素)やGaN(窒化ガリウム)などのパワー半導体は、電気自動車や再生可能エネルギーの普及に伴い、急速に市場が拡大しています。富士経済の調査によると、次世代パワー半導体は2035年に3 兆1,981 億円規模に達するとしています。

主要メーカーはスイスのSTマイクロ、米国のonsemiなどが上位を占め、日本からは三菱電機、富士電機、東芝などがランクイン。日本政府も技術開発や供給体制の強化に向け支援を進めています。

次世代半導体の将来性

次世代半導体の将来性は、現在の技術的限界を克服し、社会のあらゆる側面を根底から変革する可能性を秘めており、極めて明るいと言えます。AI、IoT、自動運転、5G/6G通信、メタバース、そして持続可能な社会の実現といった、未来の主要なトレンドを駆動する中核技術となるため、その重要性は増すばかりです。

巨大な市場成長と需要の拡大

半導体市場は今後数十年にわたって継続的な成長が見込まれており、2030年までに1兆ドル規模に達すると予測されています。この成長を牽引する最大の要因は、生成AIに代表されるAI技術の飛躍的な進化です。ChatGPTや画像生成AIなどの登場により、膨大なデータを瞬時に処理する高性能なAI半導体への需要が爆発的に高まっています。特に、AI学習用のGPU、推論処理用の専用チップ、大容量高速メモリ(HBM)などの需要は、従来の予測を大幅に上回る勢いで拡大しています。

また、次世代半導体のもう一つの重要な価値は、カーボンニュートラル社会の実現への貢献です。炭化ケイ素(SiC)や窒化ガリウム(GaN)などの新材料は、従来のシリコン半導体と比較して電力損失を70%以上削減できるため、電力変換効率の大幅な向上を実現します。

電気自動車の普及、再生可能エネルギーの大規模導入、データセンターの省電力化など、社会全体の脱炭素化が進む中で、エネルギー効率の高い次世代半導体への需要は継続的に拡大していきます。この環境価値と経済価値の両立により、次世代半導体市場は持続可能な成長軌道を描いています。

応用分野の多様化と深化

次世代半導体の応用分野は、従来のコンピュータや通信機器から、自動車、エネルギー、医療、産業機器など、社会インフラ全体に急速に拡大しています。特に自動車分野では、自動運転技術とEV化の進展により、車載半導体市場が爆発的に成長しています。自動運転では、LiDARやカメラからの膨大なセンサーデータをリアルタイムで処理するAIプロセッサが必要となり、EV化では高効率なモーター制御とバッテリー管理のためにSiCやGaNパワー半導体の需要が急増しています。

通信分野では、5G/6G通信の高速・大容量化を実現するため、GaNなどの高周波特性に優れた半導体が不可欠になっています。特に6G通信では、テラヘルツ波を使用した超高速通信が計画されており、従来の半導体技術では対応困難な領域への挑戦が始まっています。

さらに、光電融合技術により、電気信号と光信号を同一チップ上で処理する革新的な半導体の開発も進んでおり、データセンター間の超高速通信やエッジコンピューティングでの活用が期待されています。医療分野でも、体内埋込型デバイス、ウェアラブルヘルスモニター、AI診断システムなど、高性能かつ小型軽量な次世代半導体への需要が多様化しており、各分野での技術革新を加速させています。

国家戦略としての重要性

次世代半導体は、国家の経済安全保障と技術的優位性を左右する戦略的重要技術として位置づけられています。米中間の技術覇権競争の激化により、半導体の自給自足能力は国家の根幹に関わる課題となっており、各国が巨額の投資を行って半導体産業の強化を図っています。日本政府も2021年に策定した半導体戦略において、次世代半導体を「国家の基盤技術」として明確に位置づけ、産業競争力の回復と技術的自立を目指しています。

この戦略の中核となるのが、2022年に設立されたRapidus(ラピダス)です。トヨタ、ソニー、NTTなど日本を代表する8社が共同出資し、政府も700億円の支援を決定したこの新会社は、2nm世代の最先端ロジック半導体の量産化を目標としています。ラピダスは、IBMやimecなどの海外パートナーとの技術連携により、2027年の量産開始を目指しており、日本の半導体製造技術の復活と次世代技術での競争力確保を担っています。

また、熊本県へのTSMC誘致、パッケージング技術での日本企業の強みの活用など、総合的な半導体エコシステムの構築により、デジタル社会の基盤となる次世代半導体分野での国際競争力向上を図っています。

まとめ

次世代半導体技術は、微細化の限界を乗り越え、新材料とパッケージング技術により革新的な性能向上を実現します。AI、自動運転、カーボンニュートラル社会の実現など、未来の社会基盤を支える中核技術として、その重要性は今後ますます高まっていくでしょう。

ワールドインテックFC事業では、次世代半導体製造の最前線で活躍できる技術者を募集しています。最先端の半導体工場での製造技術、品質管理、装置メンテナンスなど、専門性の高い技術分野でキャリアを積みませんか。未経験からでも充実した研修制度でスキルアップを支援し、成長著しい半導体業界であなたの可能性を広げるお手伝いをいたします。